# R1C Series 800W Power Module Specification

# Model Number: R1CA2801A-P00A AcBel PN: FSE052-00AG

**80Plus Platinum Compliant**

Revision: SOA Release Date: 2014/11/30 Released by: Johnny Ho Change Date: Changed by:

PAGE 1 OF 22

# **REVISION LOG**

| DATE       | SECTION | REVISION | ISSUE / DESCRIPTION |

|------------|---------|----------|---------------------|

| 2014/11/30 |         | SOA      | Draft release       |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

|            |         |          |                     |

# **1. GENERAL SCOPE**

This specification describes the performance characteristic of an **800W** hot swappable AC-DC switching power supply module with a +12V main DC output and a +12Vsb auxiliary output. The power supply shall be able to operate as a single supply or in an N+1 parallel hot-plug able operation with active load sharing in an N+1 redundant configuration.

# 2. ELETRICAL PERFORMANCE

This Chapter describes the electrical requirements and performance compliances of *R1CA2801A-P* power supply.

# 2.1 POWER INPUT SPECIFICATION

# 2.1.1 AC Input Voltage

The power supply must operate within all specified limits over the following input voltage range. Harmonic distortion of up to 10% THD must not cause the power supply to go out of specified limits. The power supply shall recover to proper operation at VIN<sub>RECOVER</sub> = 85VAC +/- 4VAC input voltage.

| PARAMETER     | MIN     | RATED       | MAX     |

|---------------|---------|-------------|---------|

| Voltage (110) | 90Vrms  | 100-127Vrms | 140Vrms |

| Voltage (220) | 180Vrms | 200-240Vrms | 264Vrms |

| Frequency     | 47Hz    |             | 63Hz    |

# 2.1.1.1 HVDC Input Voltage

The power supply supports High Voltage Direct Current (HVDC) input over the C14 Inlet. Allowed HVDC input range as shown in below table and operate maximum no longer than two (2) hours. The power supply shall operate within all specified limits, when HVDC input meet requirements defined in this chapter.

| PARAMETER  | MIN                | RATED              | MAX                |

|------------|--------------------|--------------------|--------------------|

| HVDC (240) | 180V <sub>DC</sub> | 240V <sub>DC</sub> | 300V <sub>DC</sub> |

# 2.1.2 Inrush Current

The power supply must meet inrush requirements for any rated AC voltage; during turn on at any phase of AC voltage, during a single cycle AC dropout condition, during repetitive ON/OFF cycling of AC, and over the specified temperature range ( $T_{op}$ ). The peak inrush current shall be less than the ratings of its critical components (including input fuse, bulk rectifiers, and surge limiting device), but shall not exceed 35A in general.

#### 2.1.3 Input Current

The maximum input current defines the maximum possible input current to ensure the proper function of the power supply to meet all defined specifications.

| AC Input        | Max Current |

|-----------------|-------------|

| 110Vac – 127Vac | 10A         |

| 200Vac – 240Vac | 5A          |

#### 2.1.4 Input Power Factor Correction

The input Power Factor shall be greater than values defined in below table at power supply's rated output, and meet Energy Star<sup>®</sup> requirements.

| Output power | 10% load | 20% load | 50% load | 100% load |

|--------------|----------|----------|----------|-----------|

| Power factor | >0.65    | >0.80    | >0.95    | >0.95     |

Tested at 230VAC, 50Hz and 115VAC, 60Hz.

# 2.1.5 Harmonic

The harmonic input current defined in below table with various loading conditions which tested at 25 deg. C ambient condition. The input voltages are 115VAC/50Hz and 230VAC/60Hz.

| Load Condition | 10% | 20% | 50% | 100% |

|----------------|-----|-----|-----|------|

| 115VAC         | 10% | 10% | 5%  | 5%   |

| 230VAC         | 15% | 10% | 10% | 5%   |

# 2.1.6 AC line dropout

An Input line dropout is a transient condition defined as the line input to the power supply drops to 0 VAC at any phase of the AC line or DC line, for any length of time. During an Input dropout the power supply must meet dynamic voltage regulations requirements. An Input line dropout of any duration shall not cause dripping of the control signals and protection circuits. If the Input dropout lasts longer than the holdup time, the power supply should recover when VIN meets VIN <sub>recover</sub> and meet all turn on requirements. An Input dropout of any length shall not cause any damage to the power supply.

#### Holdup time until Power output goes out of regulations

| Loading | Main output | Standby output |

|---------|-------------|----------------|

| 100%    | 12mS        | 25mS           |

#### 2.1.7 Efficiency

The efficiency should be measured at 230VAC for AC input power modules only according to Climate Saver / 80Plus efficiency measurement specifications (CSCI-09-10). FAN power loss shall be excluded and need to be deducted from power input.

| Efficiency Std. | 10% load | 20% load | 50% load | 100% load |

|-----------------|----------|----------|----------|-----------|

| Platinum        | 82%      | 90%      | 94%      | 91%       |

# 2.1.8 AC Line Transient Specification

AC line transient conditions shall be defined as "sag" and "surge" conditions.

"Sag" conditions are also commonly referred to as "brownout", these conditions will be defined as the AC line voltage dropping below nominal voltage conditions.

"Surge" will be defined to refer to conditions when the AC line voltage rises above nominal voltage.

The power supply shall meet the requirements under the following AC line sag and surge conditions.

| Duration Sag |      | Operating AC voltage | Line frequency | Performance criteria         |

|--------------|------|----------------------|----------------|------------------------------|

| 0 to 1/2 AC  | 95%  | Nominal AC Voltage   | 50/60Hz        | No loss of function or       |

| cycle        |      | ranges               |                | performance                  |

| >1 AC cycle  | >30% | Nominal AC Voltage   | 50/60Hz        | Loss of function acceptable, |

|              |      | ranges               |                | self-recoverable             |

| Continues    | 10%  | Nominal AC Voltages  | 50/60Hz        | No loss of function or       |

|              |      |                      |                | performance                  |

| 0 to 1/2 AC  | 30%  | Mid-point of nominal | 50/60Hz        | No loss of function or       |

| cycle        |      | AC Voltages          |                | performance                  |

#### AC Line SAG and SURGE transient performance.

AC Line Sag and Surge (10sec interval between each sagging and surging)

#### 2.1.9 Power Recovery

The power supply shall recover automatically (auto recover) after an Input power failure. Input power failure is defined to be any loss of Input power that exceeds the dropout criteria.

#### 2.1.10 Input Line Leakage Current

The maximum leakage current to ground for power supply system shall not exceed 3.5mA when tested at 230VAC Input voltages.

# 2.1.11 Surge Immunity

The power supply shall be tested with the system for immunity to AC Unidirectional wave; 2kV line to ground and 1kV line to line, per EN 55024: 1998/A1: 2001/A2: 2003, EN 6100-4-5: Edition 1.1: 2001-04.

The pass criteria include: No unsafe operation is allowed under any condition all power supply output voltage levels to stay within proper spec levels; No change in operating state or loss of data during and after the test profile No component damage under any condition.

# 2.2 BROWNOUT

Power supply shall contain protection circuitry such that the application of an input voltage below the minimum specified in section 2.1.3 shall not cause damage to the power supply unit nor cause failure of the input fuse and overstress to any other component. In the event of shutdown due to extended brownout, the power supply shall automatically restart after the AC input is within specified limits. The voltage level between shutdown and recovery shall have a minimum of 5 VAC of voltage hysteresis, so that the power supply will not oscillate on and off due to voltage change condition. The power supply shall meet dynamic voltage regulations (Section 2.3.2) and all turn on requirements or turn off requirements while shutdown or recovery.

# 2.2.1 AC Turn off Requirements

Power supply shall go to power off state after a slow brownout condition. The brownout condition shall be tested with all valid redundant power system configurations using the system. While the power system is operating at full rated DC load, the AC line voltage shall be reduced from 90VAC/60Hz to 0VAC at a constant rate over a period of 30 minutes. Power supply shall shutdown at the AC voltage 80VAC±5VAC.

# 2.2.2 AC Turn on Requirements

Power supply shall return to normal power up state after a slow recovery condition. The recovery shall be tested in all valid redundant power system configurations. With the test loads configured for maximum system DC output in resistive mode, the AC line voltage shall be increased from 0VAC to 90VAC/60Hz at a constant rate over a period of 30 minutes. Power supply shall turn up at the AC voltage 85VAC±4VAC

# **2.3 POWER OUTPUT SPECIFICATION**

#### 2.3.1 Output Power/Currents

The following table defines the power and current rating of the **800W** power supply.

| Voltage   | VAC     | Mini | Max   | Peak  |

|-----------|---------|------|-------|-------|

| +12V main | 100-240 | 0.5A | 66.7A | 86.7A |

| +12Vsb    |         | 0.1A | 3A    | 3.9A  |

- 1. Maximum continuous total DC output power should not exceed 800W.

- 2. Maximum peak total DC output power should not exceed 1120W.

#### 2.3.2 Peak Power Condition

The power supply shall meet the following peak power conditions.

| Parameter | MIN  | NOM  | ΜΑΧ  | Condition           |

|-----------|------|------|------|---------------------|

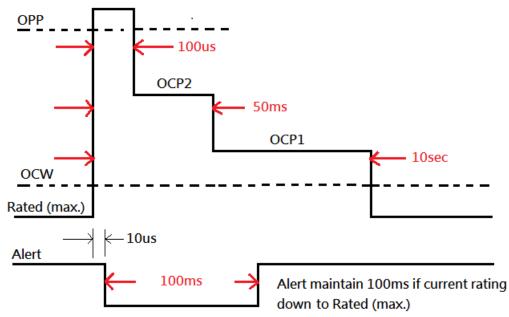

| OPP       | 140% | 145% | 150% | Keep 100uS at least |

| OCP2      | 125% | 133% | 140% | Keep 50mS at least  |

| OCP1      | 115% | 120% | 125% | Keep 10Sec at least |

| OCW       | 105% | 110% | 115% | Continue            |

| Rated     | 0%   |      | 100% | Continue            |

- Peak power condition shall be following the peak power table as specify from the above. After exceeding the max. peak power threshold of T<sub>OFF\_PEAK</sub>, the power supply will shut down in a OPP state, and according warning and failures will be reported.

- 2. The warning signal (OCW) will send to system during 105% 115% of maximum load, and shuts down after follow by the specified condition.

## 2.3.3 Voltage Regulation

The power supply shall stay within the following voltage limits when operating at steady state and dynamic loading conditions. These limits include the peak-peak ripple/noise conditions specified in paragraph 2.2.5. All outputs are measured with reference to the return remote sense (ReturnS) signal.

| Parameter | MIN    | NOM    | MAX    | Units            | Tolerance |

|-----------|--------|--------|--------|------------------|-----------|

| +12V      | +11.40 | +12.00 | +12.60 | V <sub>rms</sub> | +/-5%     |

| +12Vsb    | +11.40 | +12.00 | +12.60 | V <sub>rms</sub> | +/-5%     |

#### 2.3.4 Dynamic Loading

The power supply shall operate within specified limits and meet regulation requirements for step loading and capacitive loading specified below.

The load transient repetition rate shall be tested between 50Hz to 5kHz at duty cycles ranging from 10%-90%. The load transient repetition rate is only a test specification. The  $\Delta$  step load may occur anywhere within the MIN load and the MAX load.

| Output | <b>△Step Load Size</b> | Load Slew Rate | Capacitive Load |

|--------|------------------------|----------------|-----------------|

| +12V   | 60% of max load        | 2.0 A/μs       | 2200 μF         |

| +12Vsb | 1.0A                   | 1.0 A/µs       | 20 μF           |

Note: For dynamic condition +12V min loading is 1A.

#### 2.3.5 Capacitive Loading

The power supply shall meet all requirements with the following capacitive loading ranges.

| Output | MIN | MAX    | Units |

|--------|-----|--------|-------|

| +12V   | 500 | 36,000 | μF    |

| +12Vsb | 20  | 3,100  | μF    |

#### 2.3.6 Ripple and Noise

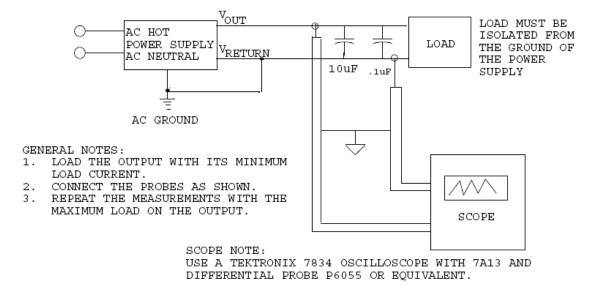

Ripple and Noise shall be measured over a Bandwidth of 20MHz at the power supply output connector, with minimum capacitive load as specified within paragraph 2.2.4 in parallel with a 10 $\mu$ F tantalum capacitor (minimum 100m  $\Omega$  ESR) and with a 0.1 $\mu$ F ceramic capacitor placed at the point of measurement. Maximum allowed ripple/noise output of the power supply is defined in table below.

| +12V      | +12Vsb    |

|-----------|-----------|

| 120 mVp-p | 120 mVp-p |

#### The test set-up shall be as shown below:

# 3. TIMING REQUIREMENTS

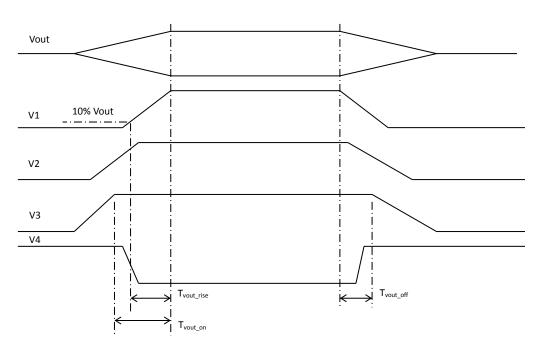

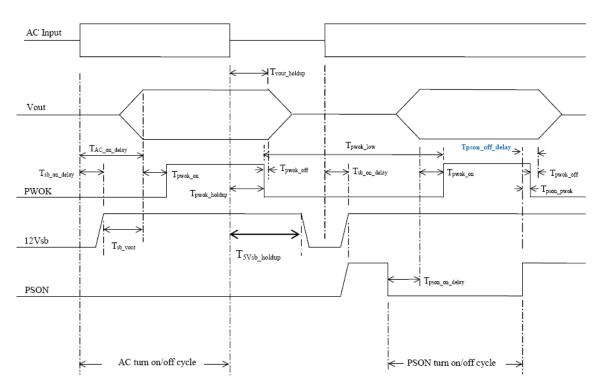

These are the timing requirements for the power supply operation. The output voltages must rise from 10% to within regulation limits (Tvout\_rise) within 5 to 70ms, and 1 to 25ms for 12Vsb. All main outputs must rise monotonically. Table below shows the timing requirements for the power supply begin turned n and off via the AC input, with PSON held low and the PSON signal, with the AC input applied.

| ltem               | Description                                  | MIN | MAX | Units |

|--------------------|----------------------------------------------|-----|-----|-------|

| <b>T</b> vout rise | Output voltage rise time for 12V main output | 5   | 70  | ms    |

|                    | Output voltage rise time for 12Vsb output    | 1   | 25  | ms    |

# **Output Voltage Timing**

# Turn On/Off Timing

| ltem                    | Description                                                                                          | MIN | MAX  | UNITS |

|-------------------------|------------------------------------------------------------------------------------------------------|-----|------|-------|

| <b>T</b> sb_on_delay    | Delay from ac begin applied to 12Vsb begin within regulation.                                        |     | 1500 | ms    |

| <b>T</b> ac_on_delay    | Delay from AC begin applied to all output voltage begin within regulation.                           |     | 3000 | ms    |

| <b>T</b> out_holdup     | Time all output voltages stay within regulation after loss of AC.                                    | 13  |      | ms    |

| <b>T</b> pwok_holdup    | Delay from loss of AC to de-assertion of PWOK.                                                       | 12  |      | ms    |

| <b>T</b> pson_off_delay | Delay from PSON# de-asserted to power<br>supply turning off                                          |     | 5    | ms    |

| <b>T</b> pson_on_delay  | Delay from PSON# active to output voltages within regulation limits.                                 | 5   | 400  | ms    |

| <b>T</b> pson_pwok      | Delay from PSON# de-active to PWOK begins de-asserted.                                               |     | 5    | ms    |

| <b>T</b> pwok_on        | Delay from output voltages within regulation<br>limits to PWOK asserted at turn on.                  |     | 500  | ms    |

| <b>T</b> pwok_off       | Delay from PWOK de-asserted to 12V output voltage dropping out of regulation limits.                 | 1   |      | ms    |

| <b>T</b> psok_low       | Duration of PWOK begin in the de-asserted state during an off/on cycle using AC or the PSON# signal. | 100 |      | ms    |

| <b>T</b> sb_vout        | Delay from 12Vsb begin in regulation to O/Ps begin in regulation at AC turn on.                      | 50  | 1000 | ms    |

| <b>T</b> 12VSB_holdup   | Time the 12VSB output voltage stays within regulation after loss of AC.                              | 70  |      | ms    |

# PAGE 10 OF 22

# Turn On/Off Timing (single Power supply)

# 4. CONTROL AND INDICATOR FUNCTIONS

The following section defines the input and output signals from the power supply. Signals that can be defined as low true use the following convention: Signal<sup>#</sup> = low true.

# 4.1 PSON<sup>#</sup> INPUT SIGNAL (POWER SUPPLY ENABLE)

The PSON<sup>#</sup> signal is required to remotely turn on/off the main output of the power supply. PSON<sup>#</sup> is an active low signal that turns on the main output power rail. When this signal is not pulled low by the system or left open, the outputs (except the Standby output) turn off. PSON<sup>#</sup> is pulled to a standby voltage by a pull-up resistor internal to the power supply.

| PSON Signal Characteristic                   |                                                                                               |         |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|---------|--|--|

| Signal Type                                  | Accepts an open collector/drain input from the system. Pull-up to VSB located in power supply |         |  |  |

| PSON <sup>#</sup> = Low                      | C                                                                                             | ON      |  |  |

| PSON <sup>#</sup> = High or Open             | 0                                                                                             | FF      |  |  |

|                                              | MIN                                                                                           | MAX     |  |  |

| Logic level low (power supply ON)            | 0V                                                                                            | 1.0V    |  |  |

| Logic level high (power supply OFF)          | 2.0V                                                                                          | 3.46V   |  |  |

| Source current, V <sub>pson</sub> = low      |                                                                                               | 4mA     |  |  |

| Power off delay: T <sub>pson_off_delay</sub> |                                                                                               | 5msec   |  |  |

| Power up delay: T <sub>pson_on_delay</sub>   | 5ms                                                                                           | 400msec |  |  |

| PWOK delay: T <sub>pson_pwok</sub>           |                                                                                               | 50msec  |  |  |

|                                              |                                                                                               |         |  |  |

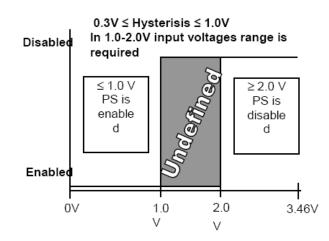

# **PSON<sup>#</sup> Signal Characteristic**

# **PSON<sup>#</sup> Signal Characteristic**

#### 4.2 POWER OK (PWOK OR PG) BUS

PWOK is a power good signal and shall be pulled HIGH by the power supply to indicate that all outputs are within regulation limits. When any output voltage falls below regulation limits, an internal failure or when AC power has been removed for a time sufficiently long, so that power supply operation is no longer guaranteed, PWOK will be de-asserted to a LOW state. The start of the PWOK delay time shall inhibited as long as any power supply output is in current limit.

| <b>_</b>                                              | <u> </u>                                                                                  |         |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|--|

| Signal Type                                           | Open collector/drain output from power supply.<br>Pull-up VSB located in the power supply |         |  |

| PWOK = High Power OK                                  |                                                                                           |         |  |

| PWOK = Low                                            | Power Not OK                                                                              |         |  |

|                                                       | MIN                                                                                       | MAX     |  |

| Logic level low voltage, $I_{sink} = 4\mu A$          | 0V                                                                                        | 0.4V    |  |

| Logic level high voltage, I <sub>source</sub> = 200µA | 2.4V                                                                                      | 3.46V   |  |

| Sink current, PWOK = low                              |                                                                                           | 400µA   |  |

| Source current, PWOK = high                           |                                                                                           | 2mA     |  |

| PWOK delay: T <sub>pwok_on</sub>                      | 100ms                                                                                     | 1000ms  |  |

| PWOK rise and fall time                               |                                                                                           | 100µsec |  |

| Power down delay: T <sub>pwok off</sub>               | 1ms                                                                                       | 200ms   |  |

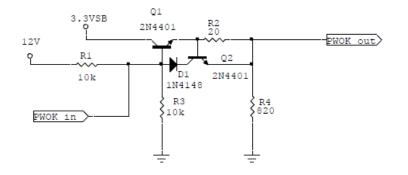

#### **PWOK / PG Signal Characteristics**

Note: The Power Ok circuits should be compatible with 5V pull up resistor (>10K) and 3.3V pull up resistor (>6.8k)

# 4.3 SMBAlert# Signal

This signal indicates that the power supply is experiencing a problem that the user should investigate. This shall be asserted due to Critical events or Warning events. The signal shall activate in the case of critical component temperature reached a warning threshold, general failure, over-current, over-voltage, under-voltage, failed fan. This signal may also indicate the power supply is reaching its end of life or is operating in an environment exceeding the specified limits.

This signal is to be asserted in parallel with LED turning solid Amber or blink Amber.

|                                          | Open collector / d    | rain output from      |  |

|------------------------------------------|-----------------------|-----------------------|--|

| Signal Type (Active Low)                 | power supply. Pull    | -up to VSB located in |  |

|                                          | system.               |                       |  |

| Alert# = High                            | ОК                    |                       |  |

| Alert# = Low                             | Power Alert to system |                       |  |

|                                          | MIN                   | MAX                   |  |

| Logic level low voltage, lsink=4 mA      | 0 V                   | 0.4 V                 |  |

| Logic level high voltage, Isink=50<br>μΑ |                       | 3.46 V                |  |

| Sink current, Alert# = low               |                       | 4 mA                  |  |

| Sink current, Alert# = high              |                       | 50 μA                 |  |

| Alert# rise and fall time                |                       | <b>100</b> μs         |  |

# 4.4 Cold Redundant\_Bus (CR\_BUS) Signal

This signal is used for power supply to power supply communication in front of an interrupt. This interrupt is by default low impedance low. For all power supplies connected to this bus shall have an open collector and a pull high circuitry, which can provide at least 4mA. This function shall be PMBus controlled and allows the system, to set the power module into four different modes:

- 1. MASTER Load dependent function

- 2. SLAVE Load dependent function

- 3. MASTER HVDC Input dependent function

- 4. SLAVE Master dependent function

SLAVE's in CR Standby shall provide PG and LED should be solid GREEN.

|                                     | Open collector / dr         | rain output from      |

|-------------------------------------|-----------------------------|-----------------------|

| Signal Type (Active HIGH)           | power supply. Pull-         | -up to VSB located in |

|                                     | system.                     |                       |

| CR_BUS# = High                      | CR Stand                    | by Allowed            |

| CR_BUS# = Low                       | SLAVEs need to be Active ON |                       |

|                                     | MIN                         | MAX                   |

| Logic level low voltage, lsink=4 mA | 0 V                         | 0.4 V                 |

| Logic level high voltage, Isource=4 |                             | 3.46 V                |

| mA                                  |                             | 5.40 V                |

| Sink current, CR_BUS# = low         |                             | 4 mA                  |

| Sink current, CR_BUS# = high        |                             | 4 mA                  |

| CR_BUS# rise and fall time          |                             | <b>100</b> μs         |

# **CR\_BUS#** Signal Characteristics

# 5. PROTECTION CIRCUITS

Protection circuits shall cause only the power supply's main outputs to shutdown (latch off). If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15 second or a PSON# cycle HIGH for 1 second must be able to reset the power supply. The auxiliary output shall not be affected by any protection circuit, unless the auxiliary output itself is affected.

# **5.1 CURRENT LIMIT**

The power supply shall prevent the main and auxiliary outputs from exceeding the values shown in below Table. If the main current limits are exceeded the power supply will shut down and latch off. The latch will be cleared by toggling the PSON# signal or by an AC power interruption. The power supply shall not be damage from repeated power cycling in this condition. *The auxiliary output shall be auto recover* (*Vsb*<sub>AR</sub>) after the OCP/SCP had been removed.

| Voltage              | Over Current Limit (lout limit) |  |

|----------------------|---------------------------------|--|

| +12V                 | 110% minimum, 150% maximum      |  |

| +12Vsb (Auxiliary)AR | 110% minimum, 150% maximum      |  |

# **5.2 FAST OUTPUT CURRENT SENSING**

The power supply shall have a circuit to quickly assert the SMBAlert signal when the output current exceeds the I<sub>throttle</sub> threshold. A current sense resistor on the output side of the PSUs output capacitors shall be used to quickly sense current exceeding the I<sub>throttle</sub> threshold. The SMBAlert# signal shall assert within Tfast\_smbalert time. The PSU shall hold the SMBAlert# signal asserted for Tsmbalert\_latch duration then release it.

Key characteristics of the fast output current sensing requirements

- Ithrottle < minimum OPP level (SMBAlert must assert before current/power hits the OPP threshold)

- Tfast\_smbalert < 10uSec

- Tsmbalert\_latch = 100mSec (+/-50mSec)

# **5.3 OVER VOLTAGE PROTECTION**

The power supply shall shutdown and latch off after an over voltage condition occurs. This latch will be cleared by toggling the PSON# signal or by an AC power interruption. A shutdown caused by an over-voltage in one power supply will not cause the other (redundant) power supply to shuts down.

The over-voltage threshold is defined in table below.

| Over Voltage Limits  |         |         |  |

|----------------------|---------|---------|--|

| Output Voltage       | MIN (V) | MAX (V) |  |

| +12V                 | 13.8    | 14.5    |  |

| +12Vsb (Auxiliary)AR | 13.3    | 14.5    |  |

# **5.3 OVER TEMPERATURE PROTECTION**

The power supply shall be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature which could cause internal part failures. In an over temperature condition the power supply shall shutdown, then recover after while the temperature back in normal condition. The 12VSB shall not shutdown during an OTP condition on the main outputs.

The temperature warning setting point is showing on below table:

| Condition         | Warning in °C | Critical in°C | Timing for SMBAlert <sup>#</sup> /LED |

|-------------------|---------------|---------------|---------------------------------------|

| T <sub>READ</sub> | 55            | 65            | 1msec                                 |

T READ: Environment Temperature

#### 6. LED IDENTIFICATION

There is one indicator LED located on the front faceplate. Status showing on below:

| Power Supply Condition                                             | LED State       |  |

|--------------------------------------------------------------------|-----------------|--|

| Output ON and OK                                                   | GREEN           |  |

| AC present / only 12Vsb on (PS off) or PSU in Cold redundant state | 1Hz Blink GREEN |  |

| AC cord unplugged or AC power lost; with a second power supply in  | AMBER           |  |

| parallel still with AC input power                                 |                 |  |

| Power supply warning events where the power supply continues to    | 1Hz Blink AMBER |  |

| operate high temp, high power, high current, slow FAN.             |                 |  |

| Power supply critical event causing a shutdown; failure, OCP, OVP, | AMBER           |  |

| FAN fail.                                                          |                 |  |

# 7. POWER SUPPLY MANAGEMENT

#### 7.1 HARD WARE LAYER

The serial bus communication devices for Power Supply Management Controller (PSMC) and Field Replacement Unit (FRU) in the power supply shall be compatible with both SMBus 2.0 "high power" and I<sup>2</sup>C Vdd based power and drive specification.

This bus shall operate at 3.3V but be tolerant to 5V pull-ups. The power supply should not have any internal pull-ups on the SMBus, pull-ups shall be located on system side. Two pins are allocated on the power supply. One pin is the serial clock (SCL). The second pin is used for serial data (SDA). Both pins are bi-directional and are used to form a serial bus. The device(s) in the power supply shall be located at an address(s) determined by addressing pins A0 and A1 on the power supply module. The circuits inside the power supply shall derive their 3.3V power from the 12VSB bus through a buffer. Device(s) shall be powered from the system side of the 12VSB or'ing device. No pull-up resistors shall be on SCL or SDA inside the power supply. The pull-up resistors should be located external to the power supply on system/application side.

#### 7.1.1 Capacitance for SMBus

The recommended Capacitance per pin on SDA and SCL shall be 10pF, and is not allowed to exceed 40pF per pin. In an N+1 configuration of up to four (4) power modules with additional PDB, the total Capacitance of each Bus pin shall not exceed 400pF.

# 7.1.2 I<sup>2</sup>C Bus Noise Requirement

The power supplies I<sup>2</sup>C Bus' SDA and SCL line shall be clean from noise, which might affect the proper function when utilized with other devices. The maximum allowed line noise on SDA or SCL is 200mV.

# 7.2 POWER SUPPLY MANAGEMENT CONTROLLER (PSMC)

The PSMC device on the PDB shall derive its power of the 12Vsb output on the system side of the O'ring device and shall be grounded to return. It shall be compatible with SMBus specification 2.0 and PMBus<sup>TM</sup> Power System Management Protocol Specification Part I and Part II in Revision 1.2 or later

It shall be located at the address set by the A0 and A1 pins.

Refer to the specification posted on <u>www.ssiforum.org</u> and <u>www.pmbus.org</u> website for details on the power supply monitoring interface requirements and refer to followed section of supported features. The below table reflect the power module addresses complying with the position in the housing.

| PDB position and PSMC address | PM1<br>B0h/B1h | PM2<br>B2h/B3h |  |

|-------------------------------|----------------|----------------|--|

| Pin A0/A1                     | 0/0            | 1/0            |  |

#### 7.3 Sensor Accuracy

The sensor of the PSMC shall meet below accuracy requirements for sensor readings. The accuracy shall be met at the specified environmental condition and the full range of rated input voltage.

#### **Sensor Accuracy Table**

|             |                              | =           |              |

|-------------|------------------------------|-------------|--------------|

| Sensor      | 10% - 20%                    | > 20% - 50% | > 50% - 100% |

|             | load                         | load        | Load         |

| Current     | ± 5%                         | ± 5%        | ± 5%         |

| Voltage     | ± 5%                         | ± 5%        | ± 5%         |

| Temperature | $\pm$ 5°C with $\Delta$ 5%   |             |              |

| FAN         | Provided by the power module |             |              |

| Input Power | ± 5% ± 5% ± 5%               |             |              |

|             | Provided by the power module |             |              |

# \*\* PMBus compliance please refer to firmware specification \*\*

PAGE 17 OF 22

# 8. ENVIRONMENTAL

#### **8.1 TEMPERATURE REQUIREMENTS**

The power supply shall operate within all specified limits over the Top temperature range. The average air temperature difference ( $\triangle T_{Ps}$ ) from the inlet to the outlet of the power supply shall not exceed the values shown below Table. All airflow shall pass through the power supply and not over the exterior surfaces of the power supply

| ITEM    | DESCRIPTION                      | MIN | MAX | UNITS |

|---------|----------------------------------|-----|-----|-------|

| Тор     | Operating temperature range.     | 0   | 50  | °C    |

| Tnon-op | Non-operating temperature range. | -40 | 70  | °C    |

#### 8.2 HUMIDITY

Operating: 10% to 95% relative humidity, non-condensing. Storage: 10% to 95% relative humidity, non-condensing.

#### 8.3 ALTITUDE

Operating: to 5,000m Non-operating: to 15,200m

#### 8.4 VIBRATION

Operating: 0.01G2/Hz at 10Hz, 0.02G2/Hz at 20Hz. Non-Operating: 0.02G2/Hz form 20Hz to 1000Hz.

#### **8.5 MECHANICAL SHOCK**

Operating: 5G, no malfunction.

Non-operating: 50G, no damage. Trapezoidal Wave, Velocity change = 4.3m/sec. Three drops in each of six directions are applied to each of the samples.

# 8.6 EMI/EMC REQUIREMENTS

The power supply shall comply with FCC part 15, CRISP 22 and EN55-22; Class A for both conducted and radiated emissions with a 3dB margin. Test shall be conducted using a shielded DC output cable to a shielded load. The load shall be adjusted to 100% load. Tests will be performed full load on each output power at 120VAC, 60Hz, and 230VAC, 50Hz.

# 9. REGULATORY REQUIREMENTS

#### 9.1 PRODUCT SAFETY COMPLIANCE

The power supply will have the following safety approvals with most current editions:

- A) UL 60950-1/CSA 60950-1 Edition 2 (USA/Canada)

- B) TUV EN60950-1 Edition 2 (Europe)

- C) IEC60950-1 Edition 2 (International)

- D) CB Certificate & Report, IEC60950-1 Edition 2

- E) CE Low Voltage Directive 2006/95/EC (Europe)

- F) BSMI (Taiwan)

- G) GB4943-2011 Certification (China)

- H) KCC (Korea)

# 9.2 ELECTROSTATIC DISCHARGE

The objective of ESD test is to determine the susceptibility and immunity of products to electrostatic discharge to which the products may be exposed, when operating under all potential environmental conditions. The test conditions and setup shall conform to that outlined in CISPR24-2 and IEC 801-2 (EN55101-2).

Air discharge: 8KV not allow error.

Contact discharge: 4KV not allow error.

Note: The above test discharge time is 1 time/sec and repeats each test 10 times.

# 9.3 HI-POT

The power supply module in the system shall be test at 1800Vac, with a trigger limit of 30mA.

# **10. RELIABILITY**

The MTBF of the power supply can be calculated with the Part-Stress Analysis method of Bell Core SR332 of the quality factors. A calculated MTBF of the power supply shall be at least 100,000 hours at 50°C ambient with 230VAC and in full load condition.

# **11. RoHS COMPLIANCE**

The directive 2002/95/EC of the European Parliament and of the Council of the 27th January 2003, on the restriction of the use of certain hazardous substances in electrical and electronic equipment, requires the reduction of the substances Lead, Mercury, Cadmium, Hexavalent Chromium, Polybrominated Biphenyls (PBB), and Polybrominated Biphenyl ethers (PBDE) in electronic products by July 1, 2006. Unless otherwise noted, all materials used will be compliant with this directive and any subsequent revisions or amendments.

PAGE 19 OF 22

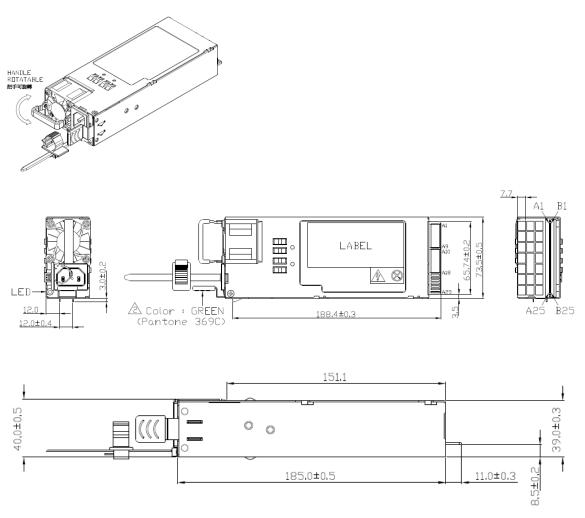

# **12. MECHANICAL DIMENSIONS**

Dimension (L x W x H): 185 x 73.5 x 40mm / 7.28 x 2.89 x 1.57inch

NOTE: Above drawing is for reference only, detail dimension should refer to independent mechanical drawing.

PAGE 20 OF 22

**R1C** Series

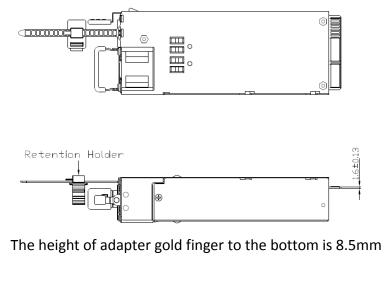

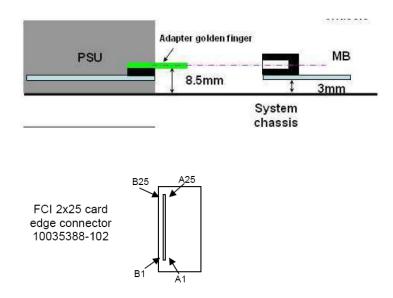

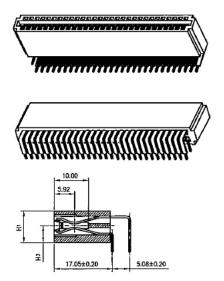

#### 12.1 DC Output connector

The power supply shall use a card edge output connection for power and signal that is compatible with a 2x25 Power Card Edge connector (equivalent to 2x25 pin configuration of the FCI power card connector 10035388-102LF or ALLTOP C21009-102H3-Y).

#### Gold finger pin assignment

#### PIN SIGNAL\_NAME SIGNAL\_NAME PIN A1 GND Β1 GND A2 B2 GND GND A3 GND B3 GND A4 GND Β4 GND A5 GND Β5 GND A6 GND Β6 GND Α7 GND Β7 GND A8 GND B8 GND A9 GND Β9 GND A10 +12V B10 +12V A11 +12V B11 +12V A12 +12V B12 +12V A13 +12V B13 +12V A14 +12V B14 +12V A15 +12V B15 +12V A16 +12V B16 +12V A17 +12V B17 +12V +12V +12V A18 B18 A19 PMBus SDA B19 A0 (SMBus address) A20 PMBus SCL B20 A1 (SMBus address) A21 PSON B21 12VSB A22 B22 SMBAlert# CR BUS# A23 Return Sense B23 12V load share Bus A24 +12V Remote Sense B24 No Connect A25 PWOK B25 NC

#### **OUTPUT PIN ASSIGNMENT**